產品分類

產品標籤

Fmuser網站

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net ->荷蘭語

- sq.fmuser.net ->阿爾巴尼亞人

- ar.fmuser.net ->阿拉伯語

- hy.fmuser.net - >亞美尼亞

- az.fmuser.net ->阿塞拜疆

- eu.fmuser.net ->巴斯克

- be.fmuser.net ->白俄羅斯語

- bg.fmuser.net - >保加利亞

- ca.fmuser.net ->加泰羅尼亞語

- zh-CN.fmuser.net ->中文(簡體)

- zh-TW.fmuser.net - >中國(繁體)

- hr.fmuser.net ->克羅地亞語

- cs.fmuser.net ->捷克

- da.fmuser.net ->丹麥語

- nl.fmuser.net - >荷蘭

- et.fmuser.net ->愛沙尼亞語

- tl.fmuser.net ->菲律賓

- fi.fmuser.net ->芬蘭語

- fr.fmuser.net - >法國

- gl.fmuser.net ->加利西亞語

- ka.fmuser.net ->喬治亞

- de.fmuser.net ->德語

- el.fmuser.net - >希臘

- ht.fmuser.net ->海地克里奧爾語

- iw.fmuser.net ->希伯來語

- hi.fmuser.net ->印地語

- hu.fmuser.net - >匈牙利

- is.fmuser.net ->冰島語

- id.fmuser.net ->印尼語

- ga.fmuser.net ->愛爾蘭

- it.fmuser.net - >意大利

- ja.fmuser.net ->日語

- ko.fmuser.net ->韓文

- lv.fmuser.net ->拉脫維亞

- lt.fmuser.net - >立陶宛

- mk.fmuser.net ->馬其頓語

- ms.fmuser.net ->馬來語

- mt.fmuser.net ->馬耳他語

- no.fmuser.net - >挪威

- fa.fmuser.net ->波斯語

- pl.fmuser.net ->波蘭語

- pt.fmuser.net ->葡萄牙語

- ro.fmuser.net - >羅馬尼亞

- ru.fmuser.net ->俄語

- sr.fmuser.net ->塞爾維亞語

- sk.fmuser.net ->斯洛伐克

- sl.fmuser.net - >斯洛文尼亞

- es.fmuser.net ->西班牙語

- sw.fmuser.net ->斯瓦希里語

- sv.fmuser.net ->瑞典語

- th.fmuser.net - >泰國

- tr.fmuser.net ->土耳其語

- uk.fmuser.net ->烏克蘭語

- ur.fmuser.net ->烏爾都語

- vi.fmuser.net - >越南

- cy.fmuser.net ->威爾士語

- yi.fmuser.net - >意第緒語

什麼是半減法器:工作及其應用,K-MAP,使用與非門的電路

Date:2021/10/18 21:55:58 Hits:

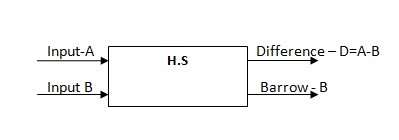

為了處理從一個點到另一個點的光或聲音等信息,我們可以通過以模擬信號的形式提供適當的輸入來使用模擬電路。 在這個過程中,輸入模擬信號有可能會拾取噪聲,這可能會導致輸出信號的損失,這意味著我們在輸入電平處理的輸入不等於輸出級。 為了,克服這些數字電路的實現。 數字電路可以用邏輯門設計。 邏輯門是一種電子電路,它根據其輸入執行邏輯運算,並只給出一個位,即低(邏輯 0 = 零電壓)或高(邏輯 1 = 高電壓)。 組合電路可以設計一個以上的邏輯門。 這些電路快速且與時間無關,在輸入和輸出之間沒有反饋。 組合電路可用於算術和布爾運算。 組合電路的最佳示例包括半加器、全加器、半減法器、全減法器、多路復用器、解復用器、編碼器和解碼器。什麼是半減法器? 如上所述的半減法器是一個組合電路,顧名思義用於從輸入中減去兩位。 這裡減法器的輸出完全依賴於當前的輸入,而不依賴於之前的階段。 半減法器的輸出是差值和手推車。 它類似於算術減法,其中如果被減數大於被減數,我們將藉用 B = 1,否則藉用將保持為零 B = 0。 為了更好地理解它,讓我們進入下面顯示的真值表。  half-subtractor-block-diagram真值表半減法器真值表根據在輸入階段應用的輸入顯示輸出值。 真值表分為兩部分。 左邊部分錶示輸入級,右邊部分錶示輸出級。在數字電路中,輸入0和輸入1表示邏輯低和邏輯高。 根據配置,邏輯低表示零電壓,邏輯高表示高電壓(如 5V、7V、12V 等)。 Inputs OutputsInput – AInput – BDifference -DBarrow – B 000010 1001111100Truth Table ExplanationWhen 輸入 A 和 B 為零,半減法器 D 和 B 的輸出也為零。當輸入 A 為高且 B 為零時,差異為高,即 1 和巴羅為零當輸入A為零,輸入B為高時,則D和B的輸出分別為高。當兩個輸入都為高時,半減法器的輸出都為零。 從上面的真值表,我們可以找出差值 (D) 和 Barrow (B) 的方程式。差值-D 的方程式:當輸入 A=1、B=0 和 A=0、B=1 時,差值是高的。 從這個陳述 D = AB'+A'B = A⊕B。 根據 D 方程,它表示 Ex-or 門。 Barrow-B 的 D=A⊕BE 方程:僅當輸入 A 為低且 B 為高時,Barro 為高。 從這一點來看,Barrow B 的方程將是, B= A'BB=A'B 從上面的差分和 Barrow 方程,我們可以使用 K -MapK 設計半減法電路圖 – MapKarnaugh 圖簡化了布爾代數表達式對於半減法器電路。 這是查找任何電路的布爾代數方程的官方方法。 讓我們使用 K-map.K-Map for Difference (D) 和 Barrow (B) 求解半減法電路的布爾表達式

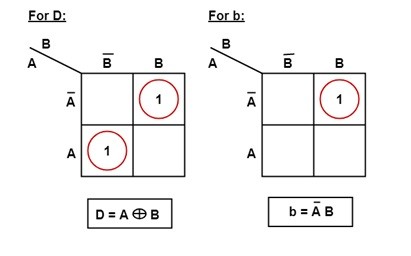

half-subtractor-block-diagram真值表半減法器真值表根據在輸入階段應用的輸入顯示輸出值。 真值表分為兩部分。 左邊部分錶示輸入級,右邊部分錶示輸出級。在數字電路中,輸入0和輸入1表示邏輯低和邏輯高。 根據配置,邏輯低表示零電壓,邏輯高表示高電壓(如 5V、7V、12V 等)。 Inputs OutputsInput – AInput – BDifference -DBarrow – B 000010 1001111100Truth Table ExplanationWhen 輸入 A 和 B 為零,半減法器 D 和 B 的輸出也為零。當輸入 A 為高且 B 為零時,差異為高,即 1 和巴羅為零當輸入A為零,輸入B為高時,則D和B的輸出分別為高。當兩個輸入都為高時,半減法器的輸出都為零。 從上面的真值表,我們可以找出差值 (D) 和 Barrow (B) 的方程式。差值-D 的方程式:當輸入 A=1、B=0 和 A=0、B=1 時,差值是高的。 從這個陳述 D = AB'+A'B = A⊕B。 根據 D 方程,它表示 Ex-or 門。 Barrow-B 的 D=A⊕BE 方程:僅當輸入 A 為低且 B 為高時,Barro 為高。 從這一點來看,Barrow B 的方程將是, B= A'BB=A'B 從上面的差分和 Barrow 方程,我們可以使用 K -MapK 設計半減法電路圖 – MapKarnaugh 圖簡化了布爾代數表達式對於半減法器電路。 這是查找任何電路的布爾代數方程的官方方法。 讓我們使用 K-map.K-Map for Difference (D) 和 Barrow (B) 求解半減法電路的布爾表達式 K-map for Difference (D) 和 Barrow (B) 根據 K-map 第一個蘊涵是 A'B,第二個蘊涵是 AB'。當我們簡化這兩個蘊涵方程時,將得到 DD 的差分的簡化方程=A'B+AB'那麼,D=A⊕B。 這個等式只是簡單地表示了異或門。要找到手推車 B 的簡化布爾表達式,我們需要遵循與差分 D 相同的過程。因此,B=A'B.Half Subtractor using NAND GatesNAND 門和或非門被稱為通用門。 在這裡,與非門被稱為通用門,因為我們可以使用 n 個與非門的組合來設計任何類型的數字電路。 由於這種特殊性,與非門被稱為通用門。 現在,我們使用與非門設計半減法器電路。

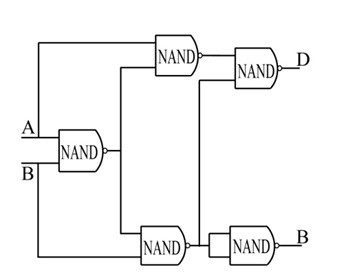

K-map for Difference (D) 和 Barrow (B) 根據 K-map 第一個蘊涵是 A'B,第二個蘊涵是 AB'。當我們簡化這兩個蘊涵方程時,將得到 DD 的差分的簡化方程=A'B+AB'那麼,D=A⊕B。 這個等式只是簡單地表示了異或門。要找到手推車 B 的簡化布爾表達式,我們需要遵循與差分 D 相同的過程。因此,B=A'B.Half Subtractor using NAND GatesNAND 門和或非門被稱為通用門。 在這裡,與非門被稱為通用門,因為我們可以使用 n 個與非門的組合來設計任何類型的數字電路。 由於這種特殊性,與非門被稱為通用門。 現在,我們使用與非門設計半減法器電路。 用與非門實現的半減法器我們可以設計具有五個與非門的半減法器電路。將 A 和 B 作為與非門第一級的輸入,其輸出再次作為一個輸入連接到第二個與非門以及第三個與非門。根據它們的輸入,它給出輸出,在與非門的最後階段,差分輸出 D 和巴羅輸出 B 將在它們的輸出端。最終的差分 D 輸出方程為 D = A ⊕B 和巴羅 B 方程為 B=A'B。通過使用不同的與非門組合來構造半減法器,差分和巴羅的最終方程將僅為 D= A⊕B 和 B=A'B。半減法器有這些減法器的各種應用。 實際上,它們很容易分析。 其中一些列如下。要減去列中最小位置的數字,這些減法器是首選。處理器中存在的算術和邏輯單元 (ALU) 更喜歡用這個單元進行減法。為了最大限度地減少聲音的失真這些被使用。根據所需的操作,半減法器具有增加或減少運算符數量的能力。半減法器用於放大器。在傳輸音頻信號時,這些用於避免失真。因此,這就是全部半減法電路。 在實時條件下,使用半減法器無法減去多個位。 這個缺點可以通過使用完整的 Subtractor 來克服。

用與非門實現的半減法器我們可以設計具有五個與非門的半減法器電路。將 A 和 B 作為與非門第一級的輸入,其輸出再次作為一個輸入連接到第二個與非門以及第三個與非門。根據它們的輸入,它給出輸出,在與非門的最後階段,差分輸出 D 和巴羅輸出 B 將在它們的輸出端。最終的差分 D 輸出方程為 D = A ⊕B 和巴羅 B 方程為 B=A'B。通過使用不同的與非門組合來構造半減法器,差分和巴羅的最終方程將僅為 D= A⊕B 和 B=A'B。半減法器有這些減法器的各種應用。 實際上,它們很容易分析。 其中一些列如下。要減去列中最小位置的數字,這些減法器是首選。處理器中存在的算術和邏輯單元 (ALU) 更喜歡用這個單元進行減法。為了最大限度地減少聲音的失真這些被使用。根據所需的操作,半減法器具有增加或減少運算符數量的能力。半減法器用於放大器。在傳輸音頻信號時,這些用於避免失真。因此,這就是全部半減法電路。 在實時條件下,使用半減法器無法減去多個位。 這個缺點可以通過使用完整的 Subtractor 來克服。

上一篇:什麼是半加器:電路圖及其應用

下一個:什麼是霍爾效應:工作及其實驗

留言

郵件列表

評論載入中...