產品分類

產品標籤

Fmuser網站

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net ->荷蘭語

- sq.fmuser.net ->阿爾巴尼亞人

- ar.fmuser.net ->阿拉伯語

- hy.fmuser.net - >亞美尼亞

- az.fmuser.net ->阿塞拜疆

- eu.fmuser.net ->巴斯克

- be.fmuser.net ->白俄羅斯語

- bg.fmuser.net - >保加利亞

- ca.fmuser.net ->加泰羅尼亞語

- zh-CN.fmuser.net ->中文(簡體)

- zh-TW.fmuser.net - >中國(繁體)

- hr.fmuser.net ->克羅地亞語

- cs.fmuser.net ->捷克

- da.fmuser.net ->丹麥語

- nl.fmuser.net - >荷蘭

- et.fmuser.net ->愛沙尼亞語

- tl.fmuser.net ->菲律賓

- fi.fmuser.net ->芬蘭語

- fr.fmuser.net - >法國

- gl.fmuser.net ->加利西亞語

- ka.fmuser.net ->喬治亞

- de.fmuser.net ->德語

- el.fmuser.net - >希臘

- ht.fmuser.net ->海地克里奧爾語

- iw.fmuser.net ->希伯來語

- hi.fmuser.net ->印地語

- hu.fmuser.net - >匈牙利

- is.fmuser.net ->冰島語

- id.fmuser.net ->印尼語

- ga.fmuser.net ->愛爾蘭

- it.fmuser.net - >意大利

- ja.fmuser.net ->日語

- ko.fmuser.net ->韓文

- lv.fmuser.net ->拉脫維亞

- lt.fmuser.net - >立陶宛

- mk.fmuser.net ->馬其頓語

- ms.fmuser.net ->馬來語

- mt.fmuser.net ->馬耳他語

- no.fmuser.net - >挪威

- fa.fmuser.net ->波斯語

- pl.fmuser.net ->波蘭語

- pt.fmuser.net ->葡萄牙語

- ro.fmuser.net - >羅馬尼亞

- ru.fmuser.net ->俄語

- sr.fmuser.net ->塞爾維亞語

- sk.fmuser.net ->斯洛伐克

- sl.fmuser.net - >斯洛文尼亞

- es.fmuser.net ->西班牙語

- sw.fmuser.net ->斯瓦希里語

- sv.fmuser.net ->瑞典語

- th.fmuser.net - >泰國

- tr.fmuser.net ->土耳其語

- uk.fmuser.net ->烏克蘭語

- ur.fmuser.net ->烏爾都語

- vi.fmuser.net - >越南

- cy.fmuser.net ->威爾士語

- yi.fmuser.net - >意第緒語

PMOS 和 NMOS 晶體管

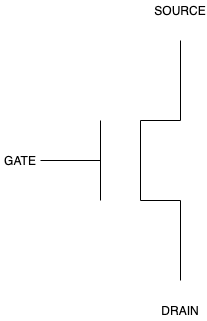

微處理器由晶體管構成。 特別是,它們由 MOS 晶體管構成。 MOS是Metal-Oxide Semiconductor的首字母縮寫。 MOS晶體管有兩種類型:pMOS(正MOS)和nMOS(負MOS)。 每個 pMOS 和 nMOS 都配備了三個主要組件:柵極、源極和漏極。

為了正確理解 pMOS 和 nMOS 的工作原理,首先定義一些術語很重要:

閉路:這意味著電流從柵極流向源極。

開路:這意味著電流沒有從柵極流向源極; 而是電流從柵極流向漏極。

當 nMOS 晶體管接收到不可忽略的電壓時,從源極到漏極的連接充當導線。 電流將不受限制地從源頭流向漏極——這被稱為閉路。 另一方面,當nMOS晶體管接收到0伏左右的電壓時,從源極到漏極的連接將斷開,這被稱為開路。

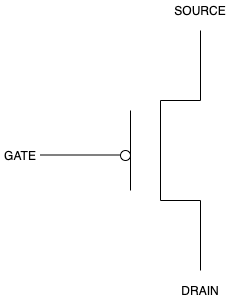

p 型晶體管的工作原理與 n 型晶體管完全相反。 而當電壓不可忽略時,nMOS將與源極形成閉合電路,而當電壓不可忽略時,pMOS將與源極形成開路。

正如您在上面顯示的 pMOS 晶體管圖像中看到的,pMOS 晶體管和 nMOS 晶體管之間的唯一區別是柵極和第一個條之間的小圓圈。 這個圓圈將電壓值反轉; 因此,如果門發送一個代表值 1 的電壓,則逆變器會將 1 更改為 0,並使電路相應地運行。

由於 pMOS 和 nMOS 以相反的方式發揮作用——互補的方式——當我們將它們組合成一個巨大的 MOS 電路時,它被稱為 cMOS 電路,它代表互補金屬氧化物半導體。

利用 MOS 電路

我們可以結合 pMOS 和 nMOS 電路來構建更複雜的結構,稱為 GATES,更具體地說:邏輯門。 我們在上一篇博客中已經介紹了這些邏輯函數的概念及其相關的真值表,您可以點擊 点击這裡.

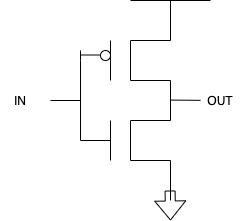

我們可以連接一個連接到源極的 pMOS 晶體管和一個連接到地的 nMOS 晶體管。 這將是我們的第一個 CMOS 晶體管示例。

這個 CMOS 晶體管的作用類似於非邏輯功能。

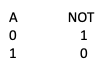

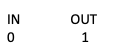

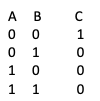

讓我們看一下 NOT 真值表:

在 NOT 真值表中,每個輸入值: A 被反轉。 上面的電路會發生什麼?

好吧,讓我們假設輸入是 0。

0 進入並在導線上上下移動到 pMOS(頂部)和 nMOS(底部)。 當值 0 到達 pMOS 時,它被反轉為 1; 因此,與源的連接已關閉。 只要與地(漏極)的連接也沒有關閉,這將產生一個邏輯值 1。 好吧,由於晶體管是互補的,我們知道 nMOS 晶體管不會反轉值; 因此,它按原樣取值 0,並且將 - 因此 - 對地(漏極)產生開路。 因此,為門生成邏輯值 1。

如果 1 是 IN 值會發生什麼? 好吧,按照與上述相同的步驟,值 1 被發送到 pMOS 和 nMOS。 當 pMOS 接收到該值時,該值被反轉為 0; 因此,與 SOURCE 的連接是打開的。 當 nMOS 接收到該值時,該值不會被反轉; 因此,該值保持為 1。當 nMOS 接收到值 1 時,關閉連接; 因此,與地面的連接關閉。 這將產生一個邏輯值 0。

將兩組輸入/輸出放在一起產生:

很容易看出,這個真值表與邏輯函數 NOT 產生的真值表完全相同。 因此,這被稱為非門。

我們可以用這兩個簡單的晶體管來製作更複雜的結構嗎? 絕對地! 接下來,我們將構建一個 NOR 門和一個 OR 門。

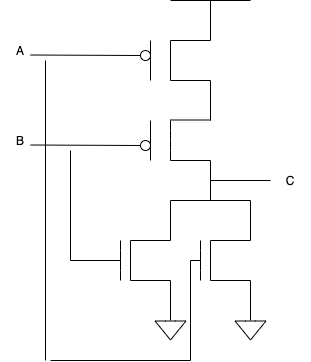

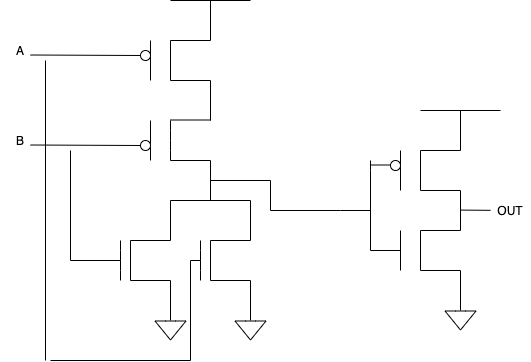

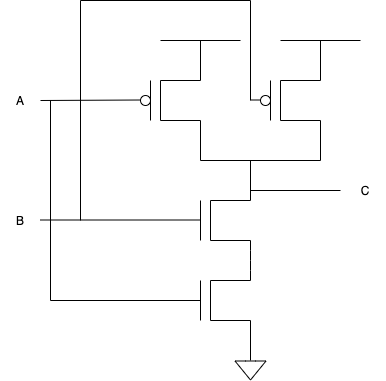

該電路在頂部使用兩個 pMOS 晶體管,在底部使用兩個 nMOS 晶體管。 再一次,讓我們看看門的輸入,看看它是如何表現的。

當 A 為 0 且 B 為 0 時,當它們到達 pMOS 晶體管時,此門將兩個值反轉為 1; 但是,nMOS 晶體管都將保持 0 的值。這將導致柵極產生 1 的值。

當 A 為 0 且 B 為 1 時,當它們到達 pMOS 晶體管時,此門將反轉這兩個值; 所以,A 會變成 1,B 會變成 0。這不會導致源; 因為兩個晶體管都需要一個閉合電路才能將輸入連接到源極。 nMOS晶體管不反轉值; 因此,與 A 關聯的 nMOS 將產生 0,與 B 關聯的 nMOS 將產生 1; 因此,與 B 相關的 nMOS 將對地產生閉合電路。 這將導致門產生 0 值。

當 A 為 1 且 B 為 0 時,當它們到達 pMOS 晶體管時,此門將反轉這兩個值; 所以,A 將變為 0,B 將變為 1。這不會導致源; 因為兩個晶體管都需要一個閉合電路才能將輸入連接到源極。 nMOS晶體管不反轉值; 因此,與 A 關聯的 nMOS 將產生 1,與 B 關聯的 nMOS 將產生 0; 因此,與 A 相關的 nMOS 將對地產生閉合電路。 這將導致門產生 0 值。

當 A 為 1 且 B 為 1 時,當它們到達 pMOS 晶體管時,此門將反轉這兩個值; 所以,A 將變為 0,B 將變為 0。這不會導致源; 因為兩個晶體管都需要一個閉合電路才能將輸入連接到源極。 nMOS晶體管不反轉值; 因此,與 A 關聯的 nMOS 將產生 1,與 B 關聯的 nMOS 將產生 1; 因此,與 A 關聯的 nMOS 和與 B 關聯的 nMOS 將對地產生閉合電路。 這將導致門產生 0 值。

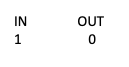

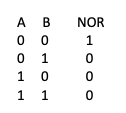

因此,門的真值表如下:

同時,NOR邏輯函數的真值表如下:

因此,我們已經確認這個門是一個 NOR 門,因為它與 NOR 邏輯函數共享它的真值表。

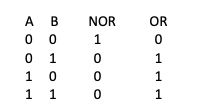

現在,我們將把迄今為止創建的兩個門放在一起,以生成 OR 門。 請記住,NOR 代表 NOT OR; 所以,如果我們反轉一個已經反轉的門,我們會得到原來的。 讓我們對其進行測試,以便看到它的實際效果。

我們在這裡所做的是我們採用了之前的 NOR 門並將 NOT 門應用於輸出。 如上所示,非門將取值 1 並輸出 0,非門將取值 0 並輸出 1。

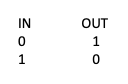

這將獲取 NOR 門的值並將所有 0 轉換為 1 並將 1 轉換為 0。 因此,真值表如下:

如果您想更多地練習測試這些門,請隨意嘗試上述值,看看門會產生相同的結果!

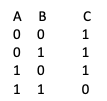

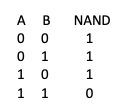

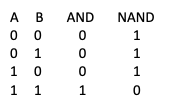

我聲稱這是一個與非門,但讓我們測試這個門的真值表以確定它是否真的是一個與非門。

當A為0,B為0時,A的pMOS會產生1,A的nMOS會產生0; 因此,該門將產生邏輯 1,因為它通過閉合電路連接到源極並通過開路與地斷開連接。

當A為0,B為1時,A的pMOS會產生1,A的nMOS會產生0; 因此,該門將產生邏輯 1,因為它通過閉合電路連接到源極並通過開路與地斷開連接。

當A為1,B為0時,B的pMOS會產生1,B的nMOS會產生0; 因此,該門將產生邏輯 1,因為它通過閉合電路連接到源極並通過開路與地斷開連接。

當A為1,B為1時,A的pMOS會產生0,A的nMOS會產生1; 所以,我們也必須檢查 B 的 pMOS 和 nMOS。 B的pMOS會產生0,B的nMOS會產生1; 因此,該門將產生邏輯 0,因為它通過開路與源斷開連接,並通過閉路連接到地。

真值表如下:

同時,NAND邏輯函數的真值表如下:

因此,我們已經驗證這確實是一個與非門。

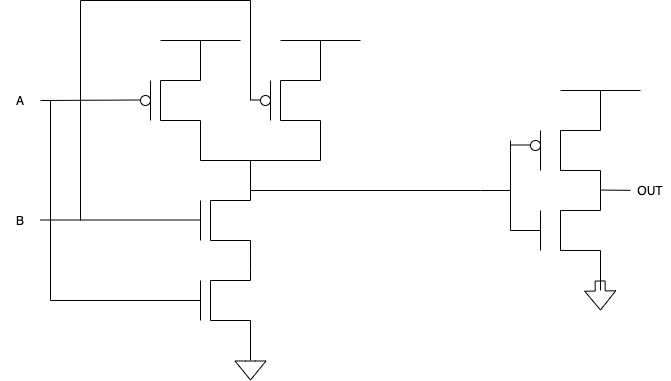

現在,我們如何建立一個與門? 好吧,我們將構建一個 AND 門,就像我們從一個 NOR 門構建一個 OR 門一樣! 我們將安裝一個逆變器!

由於我們所做的只是將 NOT 函數應用於 NAND 門的輸出,因此真值表將如下所示:

再次,請驗證以確保我告訴您的是事實。

今天,我們已經介紹了什麼是 pMOS 和 nMOS 晶體管以及如何使用它們來構建更複雜的結構! 我希望你發現這個博客內容豐富。 如果您想閱讀我以前的博客,您將在下面找到列表。