產品分類

產品標籤

Fmuser網站

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net ->荷蘭語

- sq.fmuser.net ->阿爾巴尼亞人

- ar.fmuser.net ->阿拉伯語

- hy.fmuser.net - >亞美尼亞

- az.fmuser.net ->阿塞拜疆

- eu.fmuser.net ->巴斯克

- be.fmuser.net ->白俄羅斯語

- bg.fmuser.net - >保加利亞

- ca.fmuser.net ->加泰羅尼亞語

- zh-CN.fmuser.net ->中文(簡體)

- zh-TW.fmuser.net - >中國(繁體)

- hr.fmuser.net ->克羅地亞語

- cs.fmuser.net ->捷克

- da.fmuser.net ->丹麥語

- nl.fmuser.net - >荷蘭

- et.fmuser.net ->愛沙尼亞語

- tl.fmuser.net ->菲律賓

- fi.fmuser.net ->芬蘭語

- fr.fmuser.net - >法國

- gl.fmuser.net ->加利西亞語

- ka.fmuser.net ->喬治亞

- de.fmuser.net ->德語

- el.fmuser.net - >希臘

- ht.fmuser.net ->海地克里奧爾語

- iw.fmuser.net ->希伯來語

- hi.fmuser.net ->印地語

- hu.fmuser.net - >匈牙利

- is.fmuser.net ->冰島語

- id.fmuser.net ->印尼語

- ga.fmuser.net ->愛爾蘭

- it.fmuser.net - >意大利

- ja.fmuser.net ->日語

- ko.fmuser.net ->韓文

- lv.fmuser.net ->拉脫維亞

- lt.fmuser.net - >立陶宛

- mk.fmuser.net ->馬其頓語

- ms.fmuser.net ->馬來語

- mt.fmuser.net ->馬耳他語

- no.fmuser.net - >挪威

- fa.fmuser.net ->波斯語

- pl.fmuser.net ->波蘭語

- pt.fmuser.net ->葡萄牙語

- ro.fmuser.net - >羅馬尼亞

- ru.fmuser.net ->俄語

- sr.fmuser.net ->塞爾維亞語

- sk.fmuser.net ->斯洛伐克

- sl.fmuser.net - >斯洛文尼亞

- es.fmuser.net ->西班牙語

- sw.fmuser.net ->斯瓦希里語

- sv.fmuser.net ->瑞典語

- th.fmuser.net - >泰國

- tr.fmuser.net ->土耳其語

- uk.fmuser.net ->烏克蘭語

- ur.fmuser.net ->烏爾都語

- vi.fmuser.net - >越南

- cy.fmuser.net ->威爾士語

- yi.fmuser.net - >意第緒語

基礎知識:單端和差分信令

首先,我們必須先了解一些關於什麼是單端信號的基礎知識,然後才能了解差分信號及其特性。

單端信令

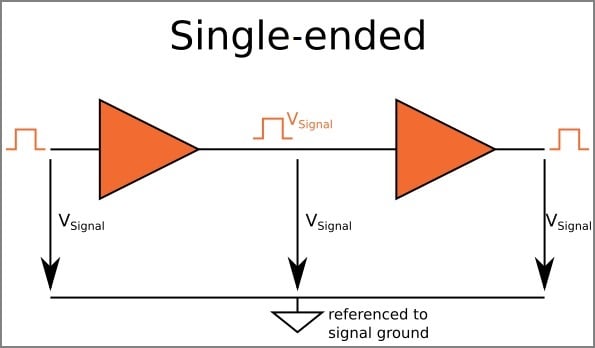

單端信令是將電信號從發送方傳輸到接收方的一種簡單而常見的方式。 電信號通過電壓(通常是變化的電壓)傳輸,該電壓以固定電位為參考,通常是稱為“地”的 0 V 節點。

一根導體承載信號,一根導體承載公共參考電位。 與信號相關的電流從發送器流向接收器,並通過接地連接返回電源。 如果傳輸多個信號,則該電路將需要為每個信號提供一根導體,外加一個共享接地連接; 因此,例如,可以使用 16 根導線傳輸 17 個信號。

單端拓撲

差分信號

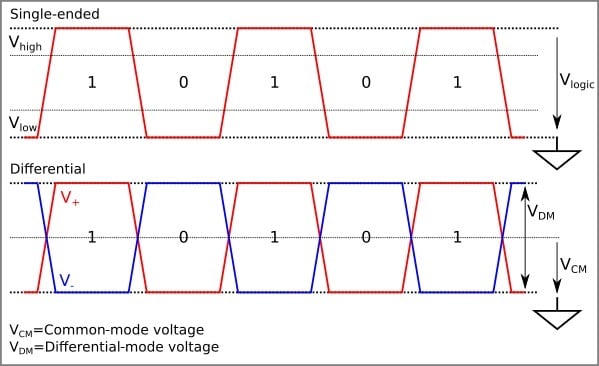

與單端信令相比,差分信令使用兩個互補的電壓信號來傳輸一個信息信號。 所以一個信息信號需要一對導體; 一個承載信號,另一個承載反相信號。

單端與差分:通用時序圖

接收器通過檢測反相信號和非反相信號之間的電位差來提取信息。 這兩個電壓信號是“平衡的”,這意味著它們相對於共模電壓具有相等的幅度和相反的極性。 與這些電壓相關的返回電流也是平衡的,因此相互抵消; 因此,我們可以說差分信號(理想情況下)流過接地連接的電流為零。

對於差分信號,發送器和接收器不必共享一個公共接地參考。 但是,使用差分信號並不意味著發送器和接收器之間的地電位差對電路的操作沒有影響。

如果傳輸多個信號,則每個信號都需要兩個導體,並且通常需要或至少有利於包括接地連接,即使所有信號都是差分的。 因此,例如,傳輸 16 個信號將需要 33 個導體(相比之下,單端傳輸需要 17 個)。 這證明了差分信號的明顯缺點。

差分信令拓撲

差分信號的好處

然而,差分信號的重要優勢不僅可以彌補導體數量的增加。

無返回電流

由於我們(理想情況下)沒有返回電流,因此接地參考變得不那麼重要。 發送器和接收器的接地電位甚至可以不同,或者在某個可接受的範圍內移動。 但是,您需要小心,因為直流耦合差分信號(例如 USB、RS-485、CAN)通常需要共享接地電位,以確保信號保持在接口的最大和最小允許共模電壓範圍內。

抗傳入 EMI 和串擾

如果從差分導體外部引入 EMI(電磁干擾)或串擾(即附近信號產生的 EMI),它會同等地添加到反相和非反相信號中。 接收器響應兩個信號之間的電壓差而不是單端(即,接地參考)電壓,因此接收器電路將大大降低干擾或串擾的幅度。

這就是為什麼差分信號對 EMI、串擾或耦合到差分對的兩個信號中的任何其他噪聲不太敏感的原因。

減少輸出 EMI 和串擾

快速轉換,例如數字信號的上升沿和下降沿,會產生大量的 EMI。 單端和差分信號都會產生 EMI,但差分對中的兩個信號會產生(理想情況下)幅度相等但極性相反的電磁場。 這與在兩個導體之間保持緊密接近的技術(例如使用雙絞線電纜)相結合,可確保來自兩個導體的輻射在很大程度上相互抵消。

低電壓操作

單端信號必須保持相對較高的電壓,以確保足夠的信噪比 (SNR)。 常見的單端接口電壓為 3.3 V 和 5 V。由於它們提高了抗噪聲能力,差分信號可以使用較低的電壓並仍然保持足夠的 SNR。 此外,相對於等效單端實現,差分信號的 SNR 會自動增加兩倍,因為差分接收器的動態範圍是差分對內每個信號的動態範圍的兩倍。

使用較低的信號電壓成功傳輸數據的能力帶來了一些重要的好處:

- 可以使用較低的電源電壓。

-

較小的電壓轉換

- 降低輻射EMI,

- 降低功耗,以及

- 允許更高的工作頻率。

高或低狀態和精確定時

您有沒有想過我們如何準確地確定信號是處於邏輯高電平還是邏輯低電平狀態? 在單端系統中,我們必須考慮電源電壓、接收器電路的閾值特性,或許還有參考電壓的值。 當然,還有一些變化和公差,這給邏輯高或邏輯低的問題帶來了額外的不確定性。

在差分信號中,確定邏輯狀態更為直接。 如果非反相信號的電壓高於反相信號的電壓,則為邏輯高。 如果非反相電壓低於反相電壓,則邏輯低。 而這兩種狀態之間的轉變就是非反相信號和反相信號相交的點——即交叉點。

這就是為什麼匹配傳輸差分信號的導線或走線的長度很重要的原因之一:為了獲得最大的時序精度,您希望交叉點與邏輯轉換完全對應,但是當線對中的兩個導體不相等時長度,傳播延遲的差異將導致交叉點移動。

應用

目前有許多采用差分信號的接口標準。 其中包括:

- LVDS(低壓差分信號)

- CML(電流模式邏輯)

- RS485

- RS422

- 乙太網路 - ENET

- CAN

- USB

- 高品質平衡音頻

顯然,差分信號的理論優勢已在無數實際應用中得到實際應用的證實。

佈線差分走線的基本 PCB 技術

最後,讓我們了解如何在 PCB 上佈線差分走線的基礎知識。 路由差分信號可能有點複雜,但有一些基本規則可以使過程更簡單。

長度和長度匹配 - 保持相等!

差分信號(理想情況下)大小相等,極性相反。 因此,在理想情況下,沒有淨返回電流流過地。 沒有返回電流是一件好事,因此我們希望一切都盡可能理想,這意味著我們需要差分對中的兩條跡線的長度相等。

信號的上升/下降時間越高(不要與信號頻率混淆),就越需要確保走線具有相同的長度。 您的佈局程序可能包含一項功能,可幫助您微調差分對的走線長度。 如果您難以達到相同的長度,您可以使用“曲折”技術。

曲折軌蹟的示例

寬度和間距——保持不變!

差分導體越接近,信號的耦合就越好。 生成的 EMI 將更有效地抵消,接收到的 EMI 將更均勻地耦合到兩個信號中。 所以試著把它們拉得很近。

您應該將差分對導體盡可能遠離相鄰信號,以避免干擾。 應根據目標阻抗選擇走線的寬度和間距,並應在整個走線長度上保持恆定。 因此,如果可能,走線在 PCB 上移動時應保持平行。

阻抗——最小化變化!

在設計帶有差分信號的 PCB 時,最重要的事情之一是找出應用的目標阻抗,然後相應地佈置差分對。 此外,盡量保持阻抗變化小。

差分線的阻抗取決於走線寬度、走線耦合、銅厚度以及 PCB 材料和層堆疊等因素。 當您嘗試避免任何改變差分對阻抗的事情時,請考慮其中的每一個。

不要在平面層上的銅區域之間的間隙上佈線高速信號,因為這也會影響您的阻抗。 盡量避免地平面的不連續性。

佈局建議——閱讀、分析和思考它們!

最後但並非最不重要的一點是,在佈線差分走線時,您必須做一件非常重要的事情:獲取發送或接收差分信號的芯片的數據表和/或應用說明,通讀佈局建議,並分析他們密切。 通過這種方式,您可以在特定設計的約束下實現最佳佈局。

結論

差分信號使我們能夠以更低的電壓、良好的 SNR、更高的抗噪聲能力和更高的數據速率傳輸信息。 另一方面,導體數量增加,系統將需要專門的發射器和接收器,而不是標準的數字 IC。

如今,差分信號已成為許多標準的一部分,包括 LVDS、USB、CAN、RS-485 和以太網,因此我們都應該(至少)熟悉這項技術。 如果您實際上是在設計帶有差分信號的 PCB,請記得查閱相關的數據表和應用筆記,如有必要,請再次閱讀本文!